產品詳情

Description

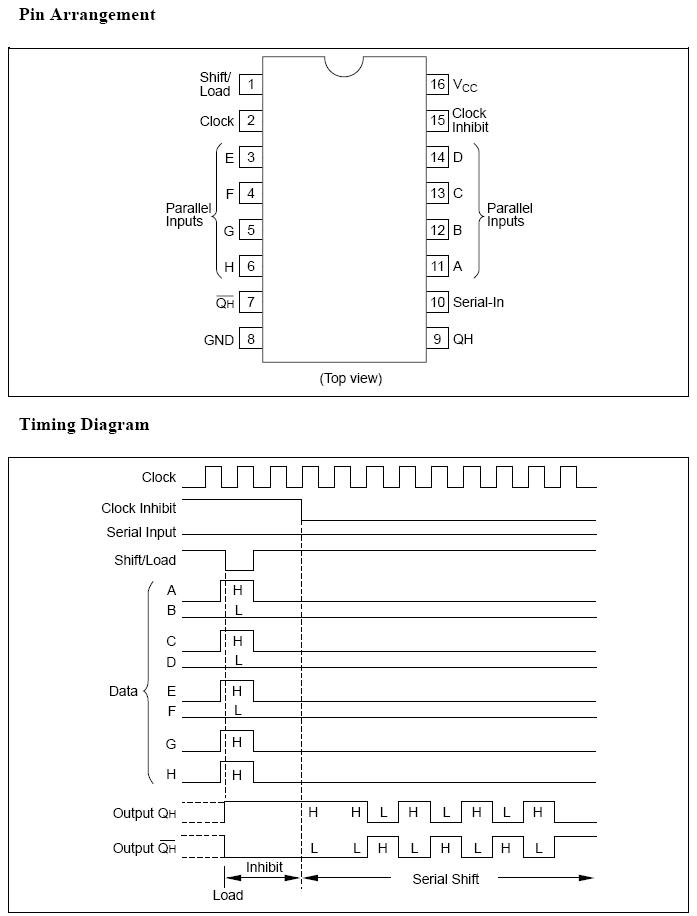

This 8-bit serial shift register shifts data from QA to QH when clocked. Parallel inputs to each stage are enabled by a low level at the Shift/Load input. Also included is a gated clock input and a complementary output from the eighth bit.

Clocking is accomplished through a 2-input NOR gate permitting one input to be used as a clock inhibit function. Holding either of the clock inputs high inhibits clocking, and holding either clock input low with the Shift/Load input high enables the other clock input. Data transfer occurs on the positive going edge of the clock. Parallel loading is inhibited as long as the Shift/Load input is high. When taken low, data at the parallel inputs is loaded directly into the register independent of the state of the clock.

Features

- High Speed Operation: tpd (Clock to QH) = 21 ns typ (CL = 50 pF)

- High Output Current: Fanout of 10 LSTTL Loads

- Wide Operating Voltage: VCC = 2 to 6 V

- Low Input Current: 1 mA max

- Low Quiescent Supply Current: ICC (static) = 4 mA max (Ta = 25°C)

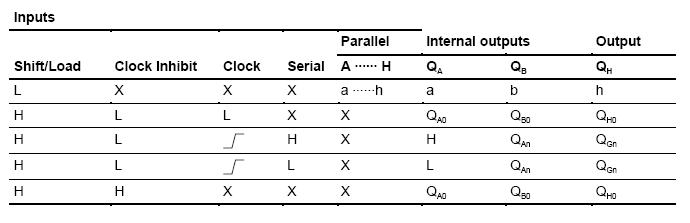

Function Table

Ordering Information

|

Part Name |

Package Type |

Package Code (Previous Code) |

Package Abbreviation |

Taping Abbreviation (Quantity) |

|

HD74HC165P |

DILP-16 pin |

PRDP0016AE-B (DP-16FV) |

P |

— |

|

HD74HC165FPEL |

SOP-16 pin (JEITA) |

PRSP0016DH-B (FP-16DAV) |

FP |

EL (2,000 pcs/reel) |

Absolute Maximum Ratings

|

Item |

Symbol |

Ratings |

Unit |

|

Supply voltage range |

VCC |

–0.5 to 7.0 |

V |

|

Input / Output voltage |

Vin, Vout |

–0.5 to VCC +0.5 |

V |

|

Input / Output diode current |

IIK, IOK |

±20 |

mA |

|

Output current |

IO |

±25 |

mA |

|

VCC, GND current |

ICC or IGND |

±50 |

mA |

|

Power dissipation |

PT |

500 |

mW |

|

Storage temperature |

Tstg |

–65 to +150 |

°C |

浙公網安備 33010502000757號

浙公網安備 33010502000757號