產品詳情

The HD74LS138 decodes one-of-eight line dependent on the conditions at the three binaly select inputs and the three enable inputs. Two active-low and one active-high enable inputs reduce the need for external gates or inverters when expanding. A 24-line decoder can be implemented without external inverters and a 32-line decoder requires only one inverter. An enable input can be used as a data input for demultiplexing applications.

Ordering Information

|

Part Name |

Package Type |

Package Code (Previous Code) |

Package Abbreviation |

Taping Abbreviation (Quantity) |

|

HD74LS138P |

DILP-16 pin |

PRDP0016AE-B (DP-16FV) |

P |

- |

|

HD74LS138FPEL |

SOP-16 pin (JEITA) |

PRSP0016DH-B (FP-16DAV) |

FP |

EL (2,000 pcs/reel) |

|

HD74LS138RPEL |

SOP-16 pin (JEDEC) |

PRSP0016DG-A (FP-16DNV) |

RP |

EL (2,500 pcs/reel) |

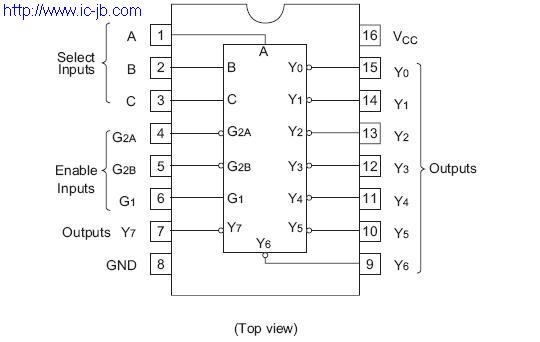

Pin Arrangement

Function Table

|

Inputs |

Outputs | |||||||||||

|

Enable |

Select | |||||||||||

|

G1 |

G2* |

C |

B |

A |

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 |

|

X |

H |

X |

X |

X |

H |

H |

H |

H |

H |

H |

H |

H |

|

L |

X |

X |

X |

X |

H |

H |

H |

H |

H |

H |

H |

H |

|

H |

L |

L |

L |

L |

L |

H |

H |

H |

H |

H |

H |

H |

|

H |

L |

L |

L |

H |

H |

L |

H |

H |

H |

H |

H |

H |

|

H |

L |

L |

H |

L |

H |

H |

L |

H |

H |

H |

H |

H |

|

H |

L |

L |

H |

H |

H |

H |

H |

L |

H |

H |

H |

H |

|

H |

L |

H |

L |

L |

H |

H |

H |

H |

L |

H |

H |

H |

|

H |

L |

H |

L |

H |

H |

H |

H |

H |

H |

L |

H |

H |

|

H |

L |

H |

H |

L |

H |

H |

H |

H |

H |

H |

L |

H |

|

H |

L |

H |

H |

H |

H |

H |

H |

H |

H |

H |

H |

L |

Absolute Maximum Ratings

|

Item |

Symbol |

Ratings |

Unit |

|

Supply voltage |

VCC |

7 |

V |

|

Input voltage |

VIN |

7 |

V |

|

Power dissipation |

PT |

400 |

mW |

|

Storage temperature |

Tstg |

–65 to +150 |

°C |

浙公網安備 33010502000757號

浙公網安備 33010502000757號